### **Programming specification**

## **About this document**

#### **Scope and purpose**

This document provides the information necessary to acquire the PSOC™ Control C3 MCU family. It describes the communication protocol required for access by an external programmer, explains the acquisition algorithm, and gives a basic description of the physical connection. Pin locations and the electrical and timing specifications of the physical connection are not a part of this document: they can be found in the device datasheet. The programming algorithms described in the following sections are compatible with all PSOC™ Control C3 MCUs.

#### **Intended audience**

This document is intended for anyone who wants to program PSOC™ Control C3 MCUs.

## **Programming specification**

## **Table of contents**

## **Table of contents**

|       | About this document                                      | 1   |

|-------|----------------------------------------------------------|-----|

|       | Table of contents                                        | 2   |

| 1     | Introduction                                             | 5   |

| 1.1   | Programmer                                               | 5   |

| 1.2   | PSOC™ Control C3 MCU family overview                     | 5   |

| 2     | Nonvolatile memory subsystem                             | 6   |

| 2.1   | Internal flash                                           | 6   |

| 2.1.1 | Dual bank mode                                           | 7   |

| 3     | Hex file                                                 | 8   |

| 3.1   | Organization of the hex file                             | 8   |

| 4     | The protocol stack                                       | 9   |

| 4.1   | Communication interface                                  | 9   |

| 4.2   | Program and debug interface                              | 9   |

| 4.2.1 | DAP power domain                                         | 10  |

| 4.2.2 | SWD/JTAG selection                                       | 10  |

| 4.2.3 | Physical layer                                           | 12  |

| 5     | Acquisition algorithm                                    | 16  |

| 5.1   | Constants and subroutines used in the acquisition flow   | 16  |

| 5.2   | DAP initialization subroutines                           | 17  |

| 5.2.1 | DAP_Handshake                                            | 17  |

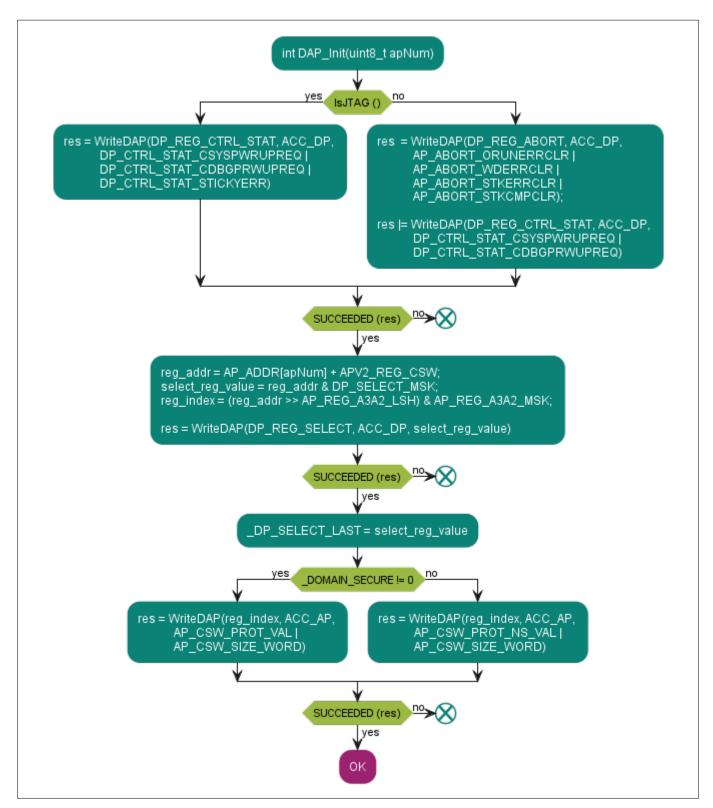

| 5.2.2 | DAP_Init                                                 | 18  |

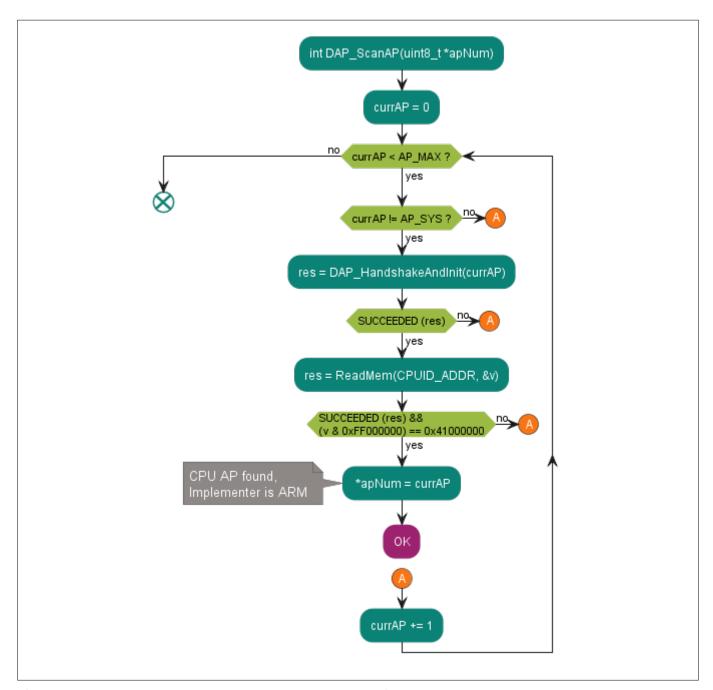

| 5.2.3 | DAP_ScanAP                                               | 19  |

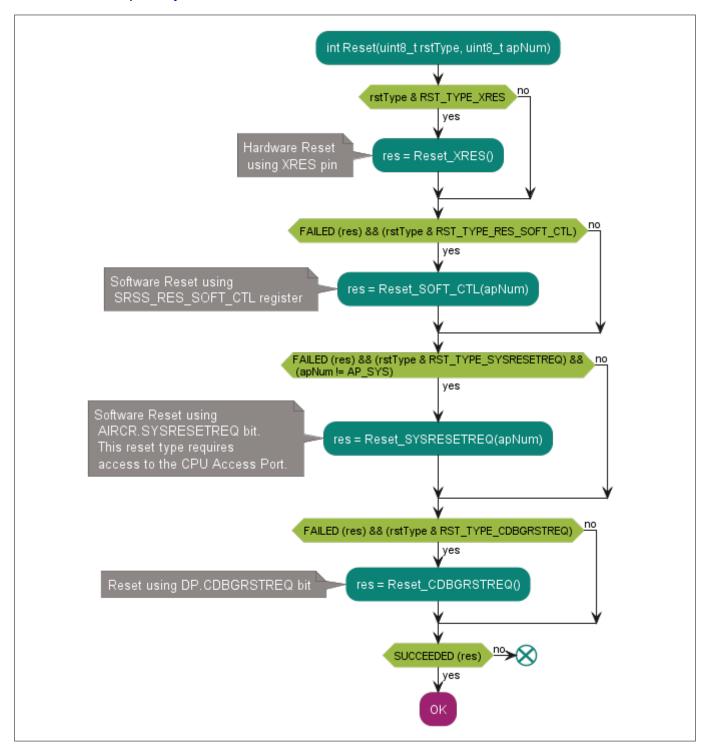

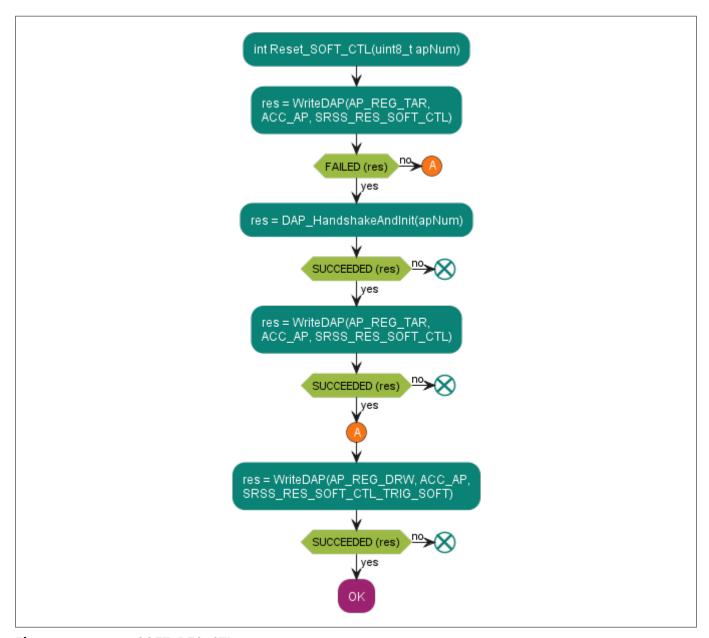

| 5.2.4 | Reset                                                    | 20  |

| 5.3   | Acquire PSOC™ Control C3 MCU                             | 24  |

| 5.3.1 | Step 1 – check boot IDLE state                           | 25  |

| 5.3.2 | Step 2 – acquire in test mode                            | 26  |

| 5.3.3 | Step 3 – acquire PSOC™ Control C3 MCU using vector catch | 29  |

| 5.4   | Unlock the access to the CPU (helper functions)          | 32  |

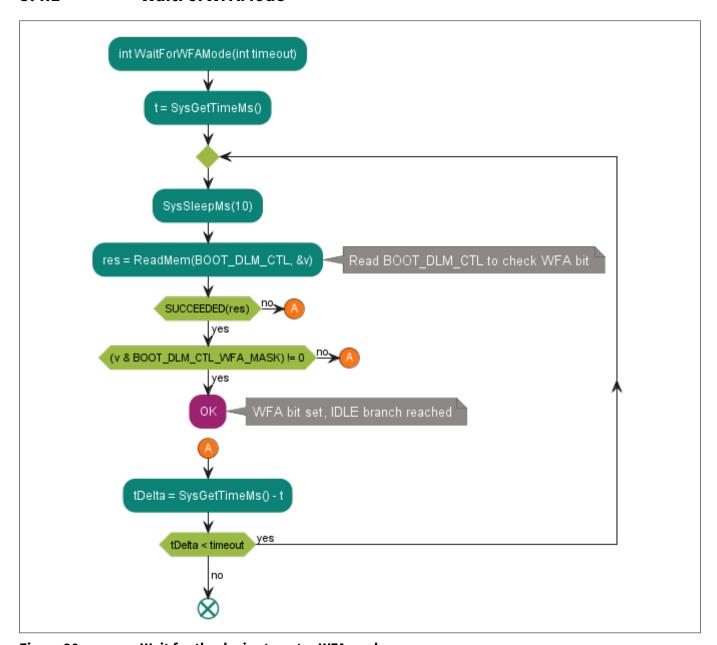

| 5.4.1 | WaitForWFAMode                                           | 33  |

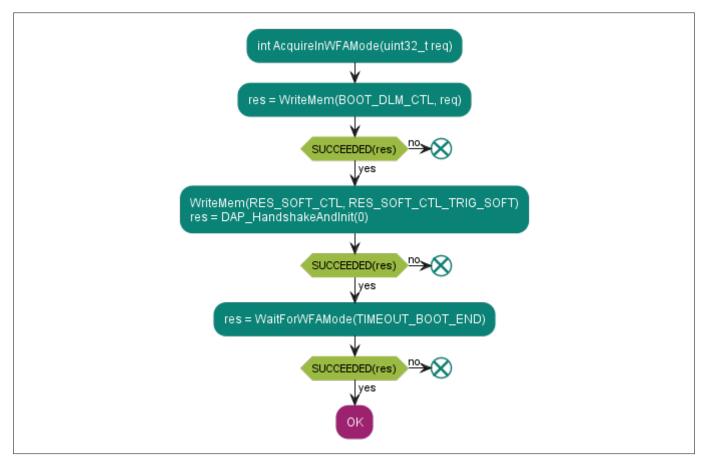

| 5.4.2 | AcquireInWFAMode                                         | 34  |

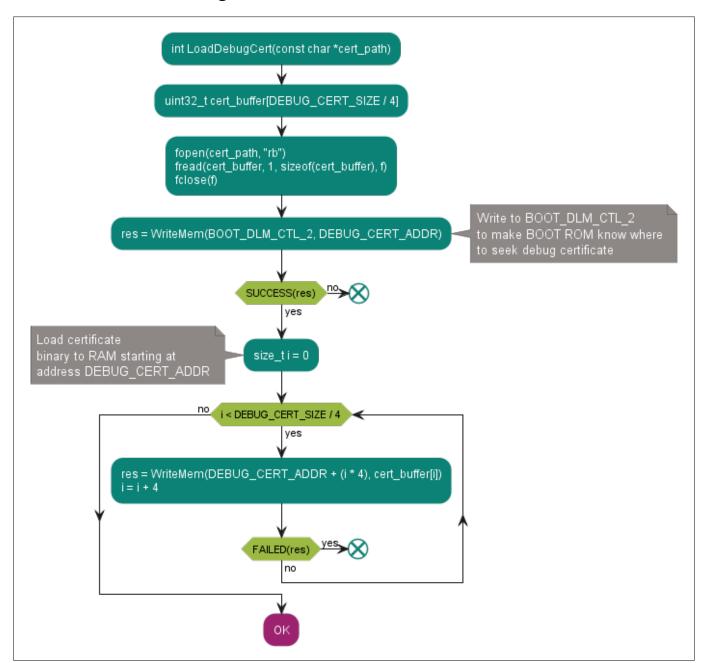

| 5.4.3 | LoadDebugCert                                            | 35  |

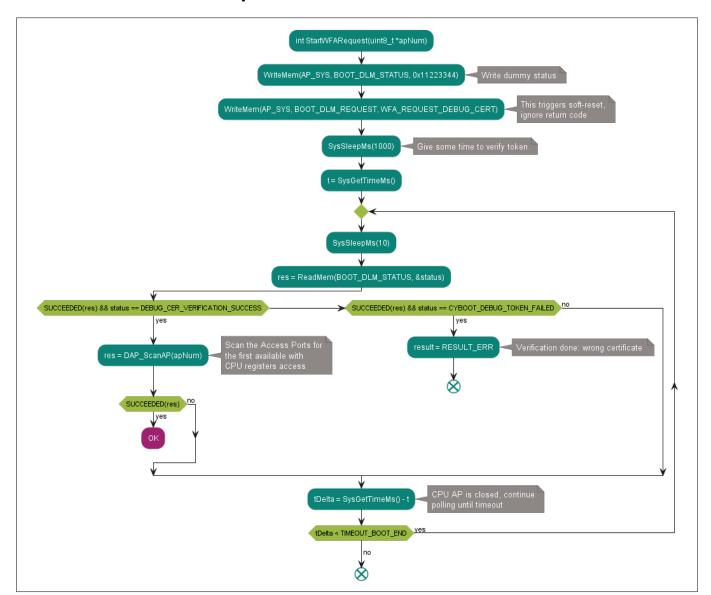

| 5.4.4 | StartWFARequest                                          | 36  |

| 5.5   | Unlock the access to the CPU using the debug certificate | 37  |

| 5.5.1 | UnlockCPUAccess                                          | 37  |

| 6     | Using SROM APIs to program/erase flash                   | 38  |

| 6.1   | SROM erases API usage                                    | 38  |

| 6.2   | SROM program API usage                                   | 3.8 |

## **Programming specification**

## infineon

## **Table of contents**

| 7       | Appendix A: Intel hex file format                           | 39 |

|---------|-------------------------------------------------------------|----|

| 8       | Appendix B: Serial wire debug (SWD) protocol                | 41 |

| 9       | Appendix C: Joint Test Action Group (JTAG) protocol         | 43 |

| 10      | Appendix D: Code example                                    | 45 |

| 10.1    | Hardware-specific backend functions                         |    |

| 10.1.1  | extern int IsJTAG(void);                                    | 45 |

| 10.1.2  | extern int SetXRES(state);                                  | 45 |

| 10.1.3  | extern int SetVoltage(voltage);                             | 45 |

| 10.1.4  | extern int SWJSequence(out_bits, num_bits);                 | 46 |

| 10.1.5  | extern int Read/WriteDAP(reg, ap_n_dp, value);              | 46 |

| 10.1.6  | extern void SysSleepMs(uint32_t msec);                      |    |

| 10.1.7  | extern int SysGetTimeMs(void);                              | 47 |

| 10.2    | Constants and static data used in code                      | 48 |

| 10.2.1  | Constants                                                   | 48 |

| 10.2.2  | Static data                                                 | 55 |

| 10.3    | Error checking functions                                    | 58 |

| 10.3.1  | SUCCEEDED                                                   | 58 |

| 10.3.2  | FAILED                                                      | 58 |

| 10.4    | DAP initialization functions                                | 59 |

| 10.4.1  | ClearStickyErrors                                           | 59 |

| 10.4.2  | DAP_Handshake                                               | 60 |

| 10.4.3  | DAP_Init                                                    | 61 |

| 10.4.4  | DAP_HandshakeAndInit                                        | 62 |

| 10.5    | Memory access and polling functions                         | 63 |

| 10.5.1  | ReadMem                                                     | 63 |

| 10.5.2  | WriteMem                                                    | 63 |

| 10.5.3  | PollMem                                                     | 64 |

| 10.6    | CPU AP lookup                                               | 65 |

| 10.6.1  | DAP_ScanAP                                                  | 65 |

| 10.7    | Arm <sup>®</sup> Core control and register access functions | 66 |

| 10.7.1  | ReadCoreReg                                                 | 66 |

| 10.7.2  | WriteCoreReg                                                | 67 |

| 10.7.3  | HaltCPU                                                     | 68 |

| 10.7.4  | ResumeCPU                                                   | 69 |

| 10.8    | System reset                                                | 70 |

| 10.8.1  | Reset                                                       | 70 |

| 10.9    | ROM Boot status checking and polling                        | 72 |

| 10.9.1  | CheckIDLE                                                   | 72 |

| 10.10   | Acquisition helper functions                                | 73 |

| 10.10.1 | AcquireTestMode                                             | 73 |

| 10.10.2 | AcquireVectorCatch                                          | 75 |

## **Table of contents**

| 10.11   | Acquisition function                            | 77 |

|---------|-------------------------------------------------|----|

| 10.11.1 | Acquire                                         | 77 |

| 10.12   | Unlocking access to the CPU, helper functions   | 79 |

| 10.12.1 | WaitForWFAMode                                  | 79 |

| 10.12.2 | AcquireInWFAMode                                | 80 |

| 10.12.3 | LoadDebugCert                                   | 81 |

| 10.12.4 | StartWFARequest                                 | 83 |

| 10.13   | Unlocking access to the CPU                     | 84 |

| 10.13.1 | UnlockCPUAccess                                 | 84 |

| 10.14   | Flash programming                               | 85 |

| 10.14.1 | SROM APIs description                           | 85 |

| 10.14.2 | Erase API usage pseudocode                      | 87 |

| 10.14.3 | Program API usage pseudocode                    | 88 |

| 10.15   | ReadAndInitSecure                               | 90 |

| 10.16   | Reads MEM-AP register of the APv2 architecture  | 91 |

| 10.17   | Writes MEM-AP register of the APv2 architecture | 92 |

|         | References                                      | 93 |

|         | Glossary                                        | 94 |

|         | Revision history                                | 95 |

|         | Disclaimer                                      | 96 |

#### **Programming specification**

#### 1 Introduction

#### 1 Introduction

This document provides the information necessary to acquire the PSOC™ Control C3 MCU family. It describes the communication protocol required for access by an external programmer, explains the acquisition algorithm, and gives a basic description of the physical connection. Pin locations and the electrical and timing specifications of the physical connection are not a part of this document: They can be found in the device datasheet. The programming algorithms described in the following sections are compatible with all PSOC™ Control C3 MCUs.

### 1.1 Programmer

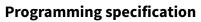

Figure 1 Programmer in development environment

In the manufacturing environment, the integrated development environment (IDE) block is absent because its main purpose is to produce a binary file (hex, elf, etc.). The programmer performs three functions:

- Parses the binary file and extracts the necessary information

- Interfaces with the silicon as a Serial Wire Debug (SWD) or JTAG master

- Implements the programming algorithm by translating the data from binary file into SWD or JTAG signals

The structure of the programmer depends on its requirements. It can be software- or firmware-centric.

In a software-centric structure, the programmer's hardware works as a bridge between the protocol (such as USB) and SWD or JTAG. An external device (software) passes all SWD/JTAG commands to the hardware through the protocol. The bridge is not involved in parsing the binary file and programming algorithm. This is the task of the upper layer (software). Examples of such programmers are MiniProg4 and Segger J-Link.

A firmware-centric structure is an independent hardware design in which all the functions of the programmer are implemented in one device, including storage for the binary file. Its main purpose is to act as a mass programmer in manufacturing.

This document does not discuss the specific implementation of the programmer. It focuses on data flow, algorithms, and physical interfacing.

#### 1.2 PSOC™ Control C3 MCU family overview

The PSOC™ Control C3 MCU family is a single-CPU utilizing the Arm® Cortex®-M33 processor core. This MCU family supports the Arm® SWJ-DP interface for programming and debugging operations, using SWD or JTAG protocols.

This document includes the following appendices:

- Appendix A: Intel hex file format

- Appendix B: Serial wire debug (SWD) protocol

- Appendix C: Joint Test Action Group (JTAG) protocol

- Appendix D: Code example

**Note**: JTAG for PSOC™ Control C3 is available if the respective configuration is set in the provisioning policy.

#### **Programming specification**

2 Nonvolatile memory subsystem

## 2 Nonvolatile memory subsystem

#### 2.1 Internal flash

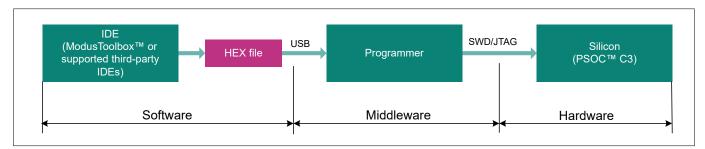

The size of the flash memory varies depending on the target. A type of the flash is NOR. A target has flash, Sflash with secure/non-secure aliases to conform to an Arm® TrustZone feature. Also, there are S-bus (read and write) and C-bus (read and execute) aliases. Offsets of flash aliases are shown in Table 1. Each macro presented in a target consists of an integer. A programmer writes one row at a time. The number of rows varies based on the size of the flash memory. A size of a row for the PSOC™ Control C3 MCU is 512 bytes. PSOC™ Control C3 MCU does not have user Sflash, which means that Sflash cannot be used to store user data.

Table 1 Flash banks for PSOC™ Control C3 MCU

| Memory | Non-secure | Secure     | Non-secure | Secure     |  |

|--------|------------|------------|------------|------------|--|

|        | C-bus      | C-bus      | S-bus      | S-bus      |  |

| SFLASH | 0x03400000 | 0x13400000 | 0x23400000 | 0x33400000 |  |

| FLASH  | 0x02000000 | 0x12000000 | 0x22000000 | 0x32000000 |  |

Also, flash memory can have row and chip level protections, refresh features, and a defined implementation. A typical flash memory structure is as shown in Figure 2.

Figure 2 Typical flash memory structure

Internal flash is programmed via SROM APIs. All these functions are blocking; that is, a processor exits only when a function is done. Pointers to necessary functions are shown in Table 2. The actual function pointer is stored at a given address.

#### **Programming specification**

#### 2 Nonvolatile memory subsystem

#### Table 2 SROM APIs for writing/erasing PSOC™ Control C3 flash memory

| Address     | Function pointer         |

|-------------|--------------------------|

| 0x1080FFE8u | cyboot_flash_write_row   |

| 0x1080FFE4u | cyboot_flash_program_row |

| 0x1080FFE0u | cyboot_flash_erase_row   |

Note:

If image to be flashed contains C-bus addresses, redirect this data to S-bus alias as it is done in official programming tools.

#### 2.1.1 Dual bank mode

PSOC™ Control C3 MCU has a dual bank mode feature. This feature divides both secure and non-secure flash banks into two parts, and second part of it has an offset of 0x800000. For example, in dual bank mode, secure flash bank is divided into:

- bank 0 0x32000000

- bank 1 0x32800000

New banks are half the size of the original bank. This feature relates to both S- and C- bus, but has nothing to do with SFlash.

To reprovision to single/dual-bank mode many times, use the Edge Protect Tools.

## **Programming specification**

3 Hex file

#### 3 Hex file

This chapter describes the information that the programmer must extract from the hex file to program the PSOC™ Control C3 MCU.

## 3.1 Organization of the hex file

The hexadecimal (hex) file describes the nonvolatile configuration of the project. It is the data source for the programmer.

The hex file for the PSOC™ Control C3 MCU follows the Intel hex file format. Intel's specification is very generic and defines only some types of records that can make up the hex file. The specification allows customizing the format for any possible silicon architecture. The silicon vendor defines the functional meaning of the records, which typically varies for different chip families. See Appendix A: Intel hex file format for details of the Intel hex file format.

## Programming specification

4 The protocol stack

## 4 The protocol stack

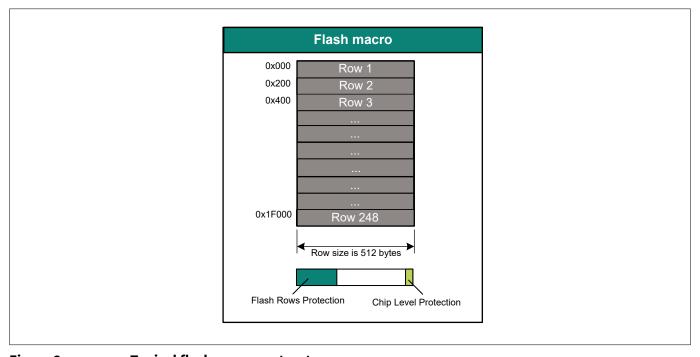

This chapter explains the low-level details of the communication interface. Figure 3 illustrates the stack of protocols involved in the programming process. The programmer must implement both hardware and software components.

Figure 3 Programmer's protocol stack

- The programming algorithm protocol, the topmost protocol, implements the whole programming flow in terms of logical and algorithmic steps. This protocol is implemented completely in software. Its smallest building block is the SWD or JTAG command. The whole programming algorithm is the meaningful flow of these blocks

- The communication interface layer acts as a bridge between pure software and hardware implementations. SWJ interface implements a set of lower-level (protocol-dependent) commands. It also transforms the software representation of these commands into line signals (digital form). The SWJ interface helps to isolate the programming algorithm from hardware specifics, which makes the algorithm reusable

- **The physical layer** is the complete hardware specification of the signals and interfacing pins and includes drive modes, voltage levels, resistance, and other components

#### 4.1 Communication interface

The external device (whether it is Infineon-supplied programmer and debugger or a third-party device that supports programming and debugging) can access most internal resources through the "Program and debug" interface provided in PSOC™ Control C3 MCU silicon. The SWD or the JTAG interface can be used as the communication protocol between the external device and the PSOC™ Control C3 MCU.

## 4.2 Program and debug interface

The main purpose of PSOC™ Control C3 MCU program and debug interface is to support programming and debugging through the JTAG or SWD interface and to provide read and write access to all memory and registers in the system while debugging, including the Cortex®-M33 register banks when the core is running or halted.

#### **Programming specification**

#### 4 The protocol stack

The PSOC™ Control C3 MCU silicon implements a DAP, which integrates SWJ-DP (serial wire/JTAG debug port) and complies with the Arm® specification "Arm® debug interface architecture specification ADIv6.0 (Arm® IHI 0074D)".

The debug physical port pins communicate with the DAP through the high-speed I/O matrix (HSIOM). The DAP communicates with the Cortex -M33 CPU using the Arm -specified advanced high-performance bus (AHB) interface. AHB is the system's interconnect protocol used inside the device, which facilitates memory and peripheral register access by the AHB master. The PSOC™ Control C3 MCU has several AHB masters, including the Arm CM33 CPU core and DAP. The external host can effectively take control of the entire device through the DAP to perform programming and debugging operations.

The debug port (DP) connects to the DAP bus, which in turn connects to one of two access ports (AP), namely:

- The CM33-AP: Located inside the CM33 core, gives access to the CM33 internal debug components. The CM33-AP port also allows access to the rest of the system through the CM33 AHB master interfaces. This provides the debug host the same view as an application running on the CM33 core

- The System-AP: Gives access to the rest of the system. This allows access to the system ROM table, which is not intended to be reached any other way. The system ROM table provides the MCU ID

#### 4.2.1 DAP power domain

Almost all the debug components are part of the active power domain. The only exception is the SWD/JTAG-DP, which is part of the Deep-Sleep power domain. This allows the debug host to connect during Deep-Sleep mode, while the application is 'running' or powered down. This enables infield debugging for low-power applications in which the chip is mostly in Deep-Sleep mode.

After the debugger is connected to the chip, it must bring the chip to the active state before any operation. For this, the SWD/JTAG-DP has a register (DP\_CTL\_STAT) with two power request bits. The two bits are:

- CDBGPWRUPREQ: Requests for debug power

- CSYSPWRUPREQ: Requests for system power

These bits must remain set for the duration of the debug session.

Note:

Only the two SWD pins (SWCLKTCK and SWDIOTMS) are operational during the Deep-Sleep mode – the JTAG pins are operational only in active mode. The JTAG debug and JTAG boundary scan are not available when the system is in Deep-Sleep mode.

#### 4.2.2 SWD/JTAG selection

JTAG and SWD are mutually exclusive because of the Arm® SWJ-DP implementation and because they share pins. Therefore, an external programmer/debugger must be able to switch to the required protocol. The watcher circuit, implemented in SWJ-DP, detects a specific 16-bit select sequence on SWDIOTMS and determines whether the JTAG or SWD interface is active. By default, JTAG operations are selected on power-on reset and therefore, the JTAG protocol can be used from reset without sending a select sequence. The protocol switching can only occur when the selected interface is in its reset state (test-logic-reset for JTAG and line-reset for SWD).

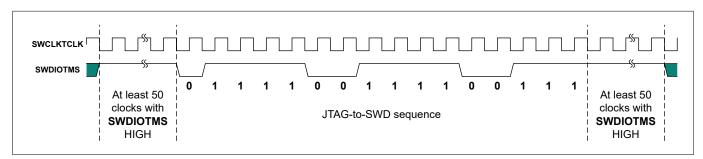

To switch SWJ-DP from JTAG to SWD operation:

Send at least 50 SWCLKTCK cycles with SWDIOTMS HIGH. This ensures that the current interface is in its

reset state. The JTAG interface detects only the 16-bit JTAG-to-SWD sequence starting from the test-logicreset state

#### **Programming specification**

#### 4 The protocol stack

- Send the 16-bit JTAG-to-SWD select sequence on SWDIOTMS: 0b0111 1001 1110 0111, most significant bit (MSB) first. This can be represented as 0x79E7, transmitted MSB first or 0xE79E, transmitted least significant bit (LSB) first

- Send at least 50 SWCLKTCK cycles with SWDIOTMS HIGH. This ensures that if SWJ-DP was already in SWD

operation before sending the select sequence, the SWD interface enters line reset state

Figure 4 JTAG-to-SWD sequence timing

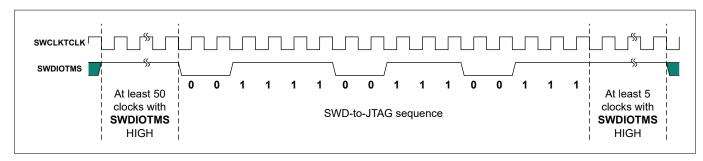

To switch SWJ-DP from SWD to JTAG operation:

- Send at least 50 SWCLKTCK cycles with SWDIOTMS HIGH. This ensures that the current interface is in its reset state. The SWD interface detects the 16-bit SWD-to-JTAG sequence only when it is in reset state

- Send the 16-bit SWD-to-JTAG select sequence on SWDIOTMS: 0b0011 1100 1110 0111, MSB first. This can be represented as 0x3CE7, transmitted MSB first, or 0xE73C, transmitted LSB first

- Send at least five SWCLKTCK cycles with SWDIOTMS HIGH. This ensures that if SWJ-DP was already in JTAG

operation before sending the select sequence, the JTAG TAP enters the test-logic-reset state

Figure 5 SWD-to-JTAG sequence timing

For a more detailed description, see the "SWD and JTAG select mechanism" section in "Arm" debug interface architecture specification ADIv6.0".

For information on the structure of the SWD read and write packets and their waveform on the bus, see Appendix B: Serial wire debug (SWD) protocol. For information on the structure of the JTAG, see Appendix C: Joint Test Action Group (JTAG) protocol.

The DAP functionally is split into two control units:

- Debug port (DP) is responsible for the physical connection to the programmer or debugger

- Access port (AP) provides the interface between the DAP module and one or more debug components (such as the Cortex -M33 CPU)

The external programmer can access the registers of these access ports using the following bits in the SWJ packet:

- APnDP select access port (0 DP, 1 AP)

- ADDR 2-bit field addressing a register in the selected access port

The SWJ read/write commands are used to access these registers. They are the smallest transactions that can appear on the SWJ bus. Table 3 shows the DAP registers that are used during programming.

#### 4 The protocol stack

Table 3 DAP registers (in Arm® notation)

| Register  | APnDP (1 bit) | Address (2-bit) | Access (R/W) | Full name                          |  |

|-----------|---------------|-----------------|--------------|------------------------------------|--|

| IDCODE    | 0             | 2'b00           | R            | Identification code register       |  |

| ABORT     | 0             | 2'b00           | W            | AP ABORT register                  |  |

| CTRL/STAT | 0             | 2'b01           | R/W          | Control/status register            |  |

| SELECT    | 0             | 2'b10           | W            | AP select register                 |  |

| RDBUFF    | 0             | 2'b11           | R            | Data buffer register               |  |

| CSW       | 1             | 2'b00           | R/W          | Control status/word register (CSW) |  |

| TAR       | 1             | 2'b01           | R/W          | Transfer address register          |  |

| DRW       | 1             | 2'b11           | R/W          | Data read/write register           |  |

For more information about these registers, see the Arm® debug interface architecture specification ADIv6.0.

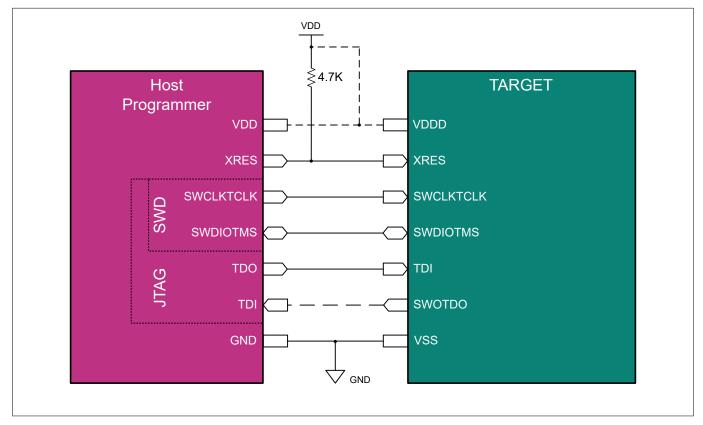

## 4.2.3 Physical layer

This section summarizes the hardware connection between the programmer and the PSOC™ Control C3 MCU for programming. Figure 6 shows the generic connection between the PSOC™ Control C3 MCU and the programmer. See Table 4 for pins/signals description.

Check the device datasheet for the part's package pins location, electrical, and timing specifications.

Figure 6 Connection schematic of the programmer

## **Programming specification**

## 4 The protocol stack

Table 4 Pins/signals

| Pin       | SWD                                         |           | JTAG                         |           | Description                                                                                                                                                                                                                                                                                                                                                            |  |

|-----------|---------------------------------------------|-----------|------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|           | Signal name                                 | Mandatory | Signal name                  | Mandatory |                                                                                                                                                                                                                                                                                                                                                                        |  |

| SWCLKTCLK | SWCLK<br>(serial wire<br>clock)             | YES       | TCLK<br>(test clock)         | YES       | Data synchronization clock, driven by the host programmer/debugger.  For SWD, the host should perform all read or write operations on the SWDIO line or the falling edge of SWDCK. The PSOC™ Control C3 MCU perform read or write operations on SWDIO on the rising edge of SWDCK.                                                                                     |  |

|           |                                             |           |                              |           | For JTAG, the host writes to the TMS and TDI pins of the PSOC™ Control C3 MCU on the falling edge of TCK and the PSOC™ Control C3 MCU reads data on it TMS and TDI lines on the rising edge of TCK. PSOC™ Control C3 MCU writes to its TDO line on the falling edge of TCK and the host reads from the TDO line of the PSOC™ Control C3 MCU on the rising edge of TCK. |  |

| SWDIOTMS  | SWDIO<br>(serial wire data<br>input/output) | YES       | TMS<br>(test mode<br>select) | YES       | SWDIO is a bidirectional data input/output signal.  TMS is the JTAG test mode selection signal, which is sampled at the rising edge of TCK to determine the next state.                                                                                                                                                                                                |  |

(table continues...)

#### **Programming specification**

# infineon

#### 4 The protocol stack

Table 4 (continued) Pins/signals

| Pin    | SWD                             |                  | JTAG                            |                  | Description                                                                                                                                                                                                                                                                                                                 |  |

|--------|---------------------------------|------------------|---------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|        | Signal name                     | Mandatory        | Signal name                     | Mandatory        |                                                                                                                                                                                                                                                                                                                             |  |

| SWOTDO | SWO<br>(serial wire<br>output)  | NO               | TDO<br>(test data<br>out)       | YES              | SWO signal (also known as TRACESWO) is required for serial wire viewer (SWV) and not required for SWD programming. It provides real-time data trace information from the PSOC™ Control C3 MCU, via the SWO pin, while the CPU continues to run at full speed. Data trace via SWV is not available using the JTAG interface. |  |

|        |                                 |                  |                                 |                  | TDO signal represents the data shifted out of the device's test or programming logic and is valid on the falling edge of TCK when the internal state machine is in the correct state.                                                                                                                                       |  |

| TDI    | -                               | -                | TDI<br>(Test Data In)           | YES              | TDI signal represents the data shifted into the device's test or programming logic. It is sampled at the rising edge of TCK.                                                                                                                                                                                                |  |

| XRES   | XRES<br>(External Reset)        | NO <sup>1)</sup> | XRES (Reset)                    | NO <sup>1)</sup> | External reset active LOW signal. The XRES is not related to the Arm® standard. It is used to reset the part as a first step in a programming flow.                                                                                                                                                                         |  |

| GND    | GND (Ground)                    | YES              | GND<br>(Ground)                 | YES              | Negative supply voltage<br>(Ground)                                                                                                                                                                                                                                                                                         |  |

| VDD    | VDD<br>(voltage drain<br>drain) | NO <sup>2)</sup> | VDD<br>(voltage<br>drain drain) | NO <sup>1)</sup> | Positive supply voltage. The PSOC™ Control C3 MCU can be powered by external power supply or by programmer.                                                                                                                                                                                                                 |  |

<sup>1)</sup> XRES pin is mandatory for "Reset" PSOC™ Control C3 MCU acquisition mode, but not used for "power cycle" mode.

You can program a chip in either reset (recommended) or power cycle mode. The mode affects only the first step - how to reset the part at the start of the programming flow. All other steps are the same.

**Reset mode**: To start programming, the host toggles the XRES line and then sends SWD/JTAG commands (see Hardware-specific subroutines section). The power on the PSOC™ Control C3 MCU board can be supplied by the host or by an external power adapter (the VDD line can be optional).

• **Power cycle mode**: To start programming, the host powers on the PSOC<sup>™</sup> Control C3 MCU and then starts sending the SW/JTAG commands. The XRES line is not used

<sup>2)</sup> VDD pin is mandatory for "power cycle" PSOC™ Control C3 MCU acquisition mode, where the programmer powers the PSOC™ Control C3 MCU and external power is not applied. For "reset" acquisition mode, the source of power supplier does not matter, so the pin is optional.

#### **Programming specification**

#### 4 The protocol stack

The programmer should implement PSOC<sup>™</sup> Control C3 MCU acquisition in reset mode. It is also the only way to acquire the PSOC<sup>™</sup> Control C3 MCU if the board consumes too much current, which the programmer cannot supply. Power cycle mode support is optional and should be used only in the following conditions:

The third-party programmer does not implement the XRES line but can supply power to the PSOC™ Control C3 MCU

### **Programming specification**

#### 5 Acquisition algorithm

## 5 Acquisition algorithm

This chapter describes in detail the programming flow of the PSOC™ Control C3 MCU. It starts with a high-level description of the algorithm and then describes every step using pseudocode. All code is based on upper-level subroutines composed of atomic SWJ instructions.

### 5.1 Constants and subroutines used in the acquisition flow

The following algorithms rely on a few low-level, hardware-specific subroutines which must be implemented by the user. This section provides only a short overview of these functions.

See Hardware-specific backend functions for details.

| Subroutine           | Description                                                                                                                                          |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| IsJTAG()             | Returns any non-zero value if the underlying transport is JTAG (zero for SWD)                                                                        |  |  |  |

| SetXRES()            | Controls the logic level on the XRES (nSRST) pin - hard reset                                                                                        |  |  |  |

| SetVoltage()         | Controls the voltage supplied by the debug adapter to power the target MCU. This function is optional and should return an error if not implemented. |  |  |  |

| SWJSequence()        | Generates the given bit sequence on the SWDIO/TMS pin, used for JTAG->SWD and SWD->JTAG switching                                                    |  |  |  |

| ReadDAP() WriteDAP() | Reads (or writes) data to the CoreSight registers                                                                                                    |  |  |  |

| SysSleepMs()         | Delays the execution by the given number of milliseconds                                                                                             |  |  |  |

| SysGetTimeMs()       | Returns the number of milliseconds that have elapsed since some fixed time point in the past                                                         |  |  |  |

See Constants and static data used in code for a detailed list of constants used by the subroutines.

The programming flow includes some operations that are used in all steps. The execution flow of these subroutines is straightforward, so only a summary table is provided here.

See Appendix D: Code example for a detailed description.

| Subroutine             | Description                                                                                     | Example              |  |

|------------------------|-------------------------------------------------------------------------------------------------|----------------------|--|

| ClearStickyErrors()    | Clears any sticky errors which could be left from previous sessions                             | ClearStickyErrors    |  |

| DAP_HandshakeAndInit() | Performs a handshake and initializes the debug port                                             | DAP_HandshakeAndInit |  |

| ReadMem()              | Reads a 32-bit value from the memory address provided                                           | ReadMem              |  |

| WriteMem(…)            | Writes a 32-bit value to the memory address provided                                            | WriteMem             |  |

| PollMem()              | Polls for the expected bit-field value in the given register                                    | PollMem              |  |

| ReadCoreReg()          | Reads the Arm <sup>®</sup> core register, special-purpose register, or floating-point register  | ReadCoreReg          |  |

| WriteCoreReg(…)        | Writes the Arm <sup>®</sup> core register, special-purpose register, or floating-point register | WriteCoreReg         |  |

| HaltCPU()              | Enables debug and halts the CPU using the DHCSR register                                        | HaltCPU              |  |

#### **Programming specification**

#### 5 Acquisition algorithm

| Subroutine           | Description                                                                                     | Example            |

|----------------------|-------------------------------------------------------------------------------------------------|--------------------|

| ResumeCPU()          | Enables debug and resumes the CPU using the DHCSR register                                      | ResumeCPU          |

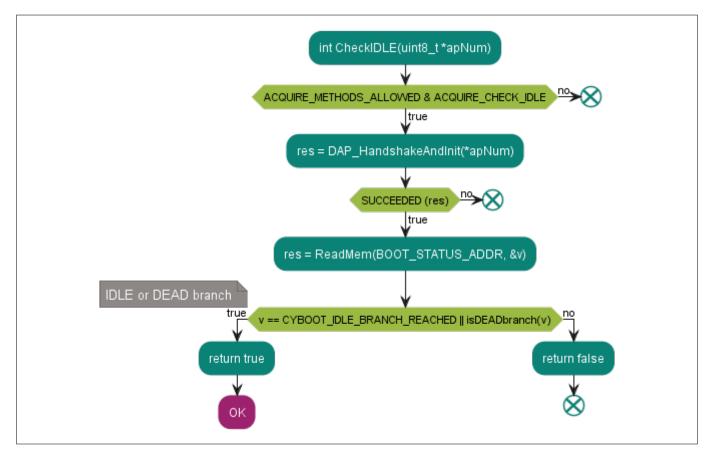

| CheckIDLE()          | Checks whether the device is in WFA (wait for action), IDLE or DEAD branches                    | CheckIDLE          |

| AcquireTestMode()    | Acquires target in test mode by setting the TST_MODE_TEST_MODE bit in the TST_MODE register     | AcquireTestMode    |

| AcquireVectorCatch() | Acquires target using the vector catch method                                                   | AcquireVectorCatch |

| WaitForWFAMode()     | Waits for the boot code to enter WFA mode used in the unlock procedure using debug certificates | WaitForWFAMode     |

| AcquireInWFAMode()   | Acquires the device in WFA mode; used in the unlock procedure using debug certificates          | AcquireInWFAMode   |

| LoadDebugCert()      | Loads the debug certificate to the RAM; used in the unlock procedure using debug certificates   | LoadDebugCert      |

| StartWFARequest()    | Starts the WFA request; used in unlock procedure using debug certificates                       | StartWFARequest    |

#### 5.2 **DAP** initialization subroutines

The very first step required to initiate a connection between the debugger and the target MCU is to initialize the DAP port. This can be achieved by using the following subroutines:

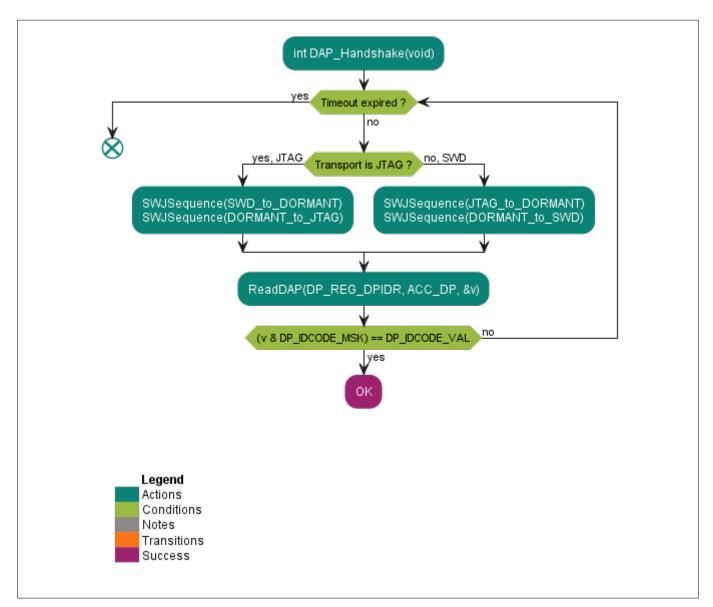

#### 5.2.1 DAP\_Handshake

Waits for the debug interface to become enabled after a device reset. Boot timing parameters are given in Table 5 and are dependent on the CPU clock used by the boot code, type of boot, and other parameters. For PowerCycle acquisition, the timeout depends on the design schematic and must be longer. See the code example provided in DAP\_Handshake.

#### **Programming specification**

#### 5 Acquisition algorithm

Figure 7 Flowchart of the DAP\_Handshake subroutine

#### 5.2.2 DAP\_Init

Initializes the debug port for programing operations. DAP must be enabled and accessible at the moment this function is called.

Accepts access port number as the input:

- 0 System AP

- 1 CM33 AP

See the code example in DAP\_Init.

#### 5 Acquisition algorithm

Figure 8 Flowchart of the DAP\_Init subroutine

#### 5.2.3 DAP\_ScanAP

Scans the access ports first available with CPU registers access. See the code example in DAP\_ScanAP.

#### 5 Acquisition algorithm

Figure 9 Flowchart of the DAP\_ScanAP subroutine

#### **5.2.4** Reset

The reset procedure is used during device acquisition; thus, it is very important for reset to reliably happen regardless of the state and hardware configuration of the target board. The most reliable reset type is hardware reset because it performs a full reset of the device including the reset of the retention registers which preserve their state between software resets.

The hardware reset signal can be routed to other (external to the MCU) peripherals on the target board. This ensures that all target systems start from the well-known state after reset.

Moreover, a hardware reset is required to perform the MCU acquisition in test mode, which is the recommended and most reliable acquisition method. It is strongly recommended to have the XRES pin properly routed to the debug connector.

#### **Programming specification**

#### 5 Acquisition algorithm

If it is not possible for the debugger to perform a hardware reset for some reason (e.g., XRES signal not connected), the reset subroutine uses several strategies to ensure that the reset is successful. These include the following:

- Hardware reset by toggling the XRES pin

- Software reset by setting the RES\_SOFT\_CTL.TRIGGER\_SOFT bit

- Software reset by setting the AIRCR.SYSRESETREQ bit

- Software reset by setting the DP->CTRL/STAT.CDBGRSTREQ bit

See the code example in System reset.

Figure 10 High-level flowchart of the reset procedure

#### 5 Acquisition algorithm

Figure 11 SOFT\_RES\_CTL reset

#### 5 Acquisition algorithm

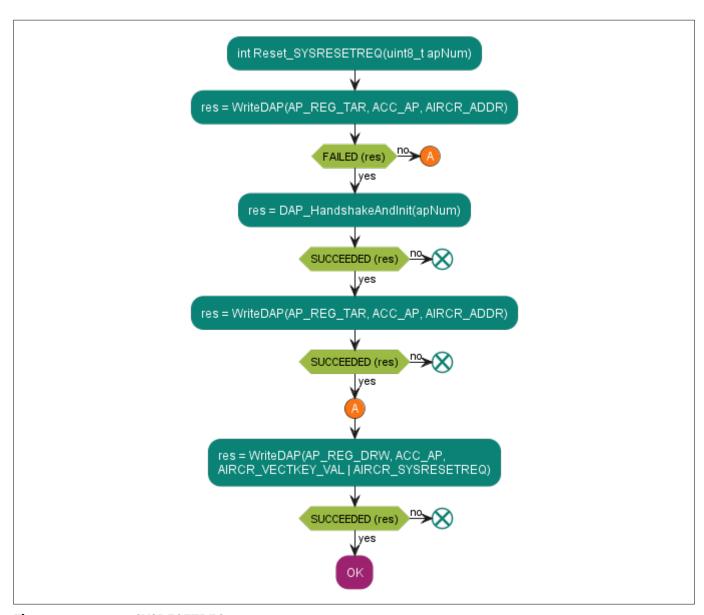

Figure 12 SYSRESETREQ reset

#### 5 Acquisition algorithm

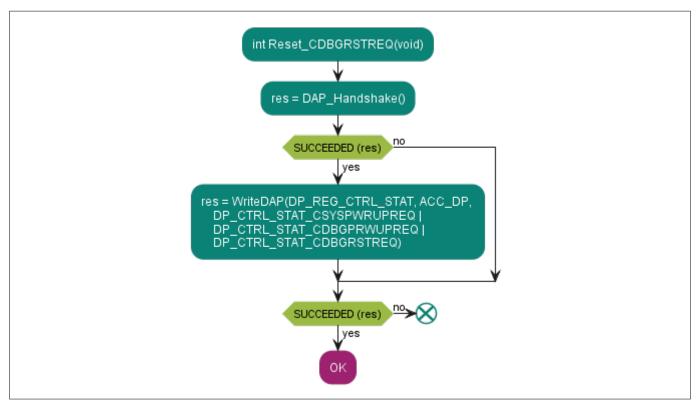

Figure 13 CDBGRSTREQ reset

#### **5.3** Acquire PSOC™ Control C3 MCU

The first step for the debugger before any programming or debugging actions is to acquire the device in a known good state and prevent execution of the user's code, which can put the MCU into a bad or corrupted state or repurpose the SWJ pins<sup>1</sup>).

There are five different steps for PSOC™ Control C3 MCU acquiring, performed by the debugger sequentially:

- 1. Check the boot IDLE state

- **2.** Acquire in test mode with hardware reset

- **3.** Acquire in test mode with software reset

- **4.** Acquire with vector catch with hardware reset

- 5. Acquire with vector catch with software reset

(use them as GPIO) such that the external debugger will not be able to communicate with the device.

The application firmware is expected to follow this procedure for SWJ pin configuration:

<sup>1.</sup> Do not modify the configuration of the SWJ pins for parts that have a permanent SWD interface. They will be properly configured and may have already connected to the SWD probe when the firmware starts

**<sup>2.</sup>** For parts that repurpose their SWD pins:

<sup>•</sup> If the SWD interface is presently active (CPUSS\_DP\_STATUS.SWJ\_CONNECTED bit is '1'), leave the pins in their current state; a probe has connected during the acquire window and the pins should not be repurposed

If the SWD interface is not active, you may configure the pins and enable the alternate purpose

#### **Programming specification**

#### 5 Acquisition algorithm

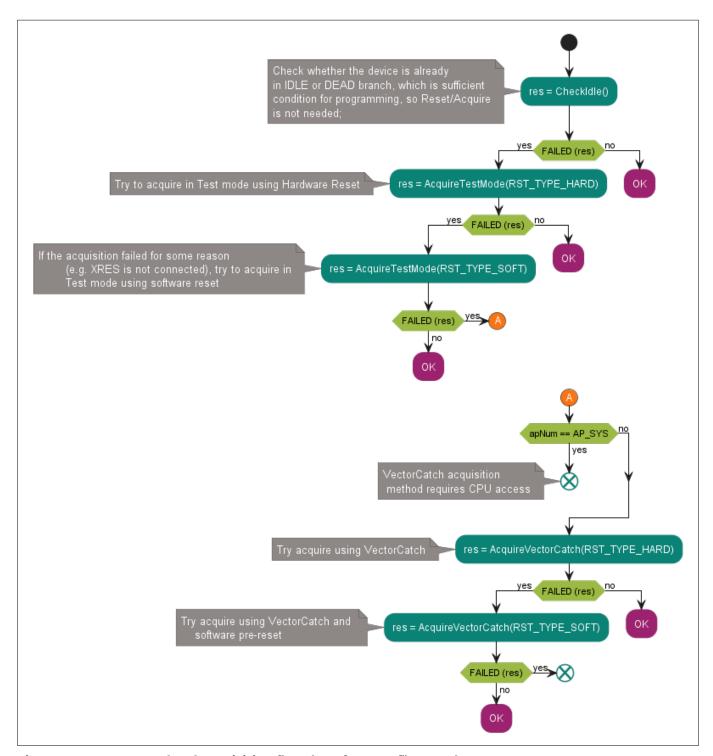

Figure 14 Top-level acquisition flowchart for PSOC™ Control C3 MCU

See the code example in AcquireVectorCatch.

#### 5.3.1 Step 1 – check boot IDLE state

The IDLE state of the PSOC™ Control C3 MCU is the state when the ROM boot code did not launch the user's application, but is executing an endless loop in one of the following branches:

IDLE branch: The boot code entered test mode or waits for the debugger for further actions in preproduction lifecycle stages such as SORT, NORMAL, or RMA

#### **Programming specification**

#### 5 Acquisition algorithm

- DEAD branch: Indicates a recoverable failure occurred (for example, an invalid TOC object, an empty flash, or an invalid app inside)

- CORRUPTED branch: Indicates that the major system failure occurred (for example, BIST failed), the debugger has limited MCU access (via system access port only), and the programming is not possible

IDLE and DEAD branches are sufficient MCU states for the debugger to perform further programming or debugging actions, so the additional device acquisition steps are not required.

**Note**: DEAD branch has many return codes.

Figure 15 Step 1 - check boot IDLE state flowchart

## 5.3.2 Step 2 – acquire in test mode

The test mode acquisition step has strict timing requirements that the host must meet to enter test mode successfully.

#### 5 Acquisition algorithm

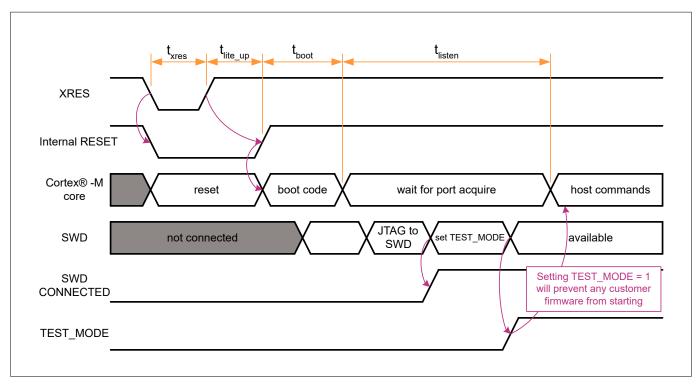

Figure 16 Timing diagram for entering test mode

This diagram details the chip's internal signals while entering test mode. Everything starts from toggling the XRES line (or applying power) so that the chip enters internal reset mode for  $t_{lite\_up}$  period. After that, the system boot code starts execution. When completed, the CPU waits during a  $t_{listen}$  period for a special connection sequence on the SWJ port. If, during this time, the host sends the correct sequence of SWJ commands, the CPU enters test mode. Otherwise, it starts the execution of the user's code. Timing parameters may vary depending on the boot code execution flow (see Table 5). Therefore, the best way to enter test mode is to start sending an acquire sequence immediately after XRES is toggled (or power is supplied in power cycle mode). This sequence is sent iteratively until it succeeds (all SWJ transactions are ACKed and all conditions are met).

Table 5 Boot timing parameters

| Parameter            | Descript                                                                                                                                                                                                                                                                          | Min                                                                                                                        | Max | Units |    |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----|-------|----|

| t <sub>lite_up</sub> | Time from                                                                                                                                                                                                                                                                         | m reset release until the CPU begins executing the e                                                                       | -   | 250   | μs |

| t <sub>boot</sub>    | Time from when the boot code started execution until it opens SWJ lines and starts waiting for the TEST_MODE sequence. This time varies depending on the CPU clock, device lifecycle stage, etc. Usually, less than 5 ms, but in the most harsh scenario, it can be up to 500 ms. |                                                                                                                            |     | 500   | ms |

| t <sub>listen</sub>  | port initia                                                                                                                                                                                                                                                                       | of time the boot code waits and listens for the SWJ alization sequence before starting the application execution.          | 0   | 100   | ms |

|                      | Note:                                                                                                                                                                                                                                                                             | The default duration of the listen window (t <sub>listen</sub> ) is 100 ms, but it may vary depending on the provisioning. |     |       |    |

Figure 16 shows the test mode acquisition procedure. It is detailed in terms of the SWD transaction.

#### **Programming specification**

#### 5 Acquisition algorithm

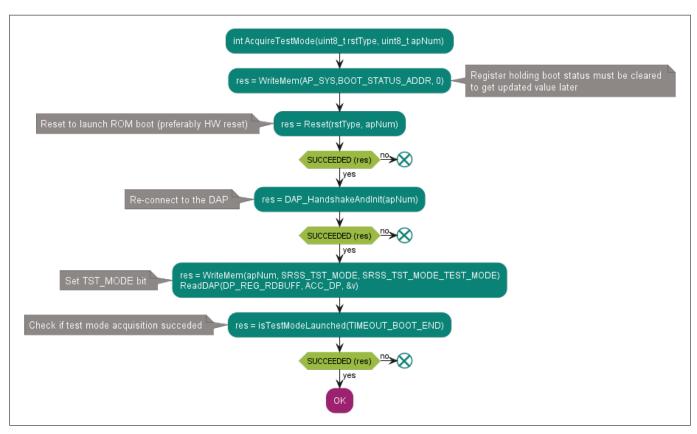

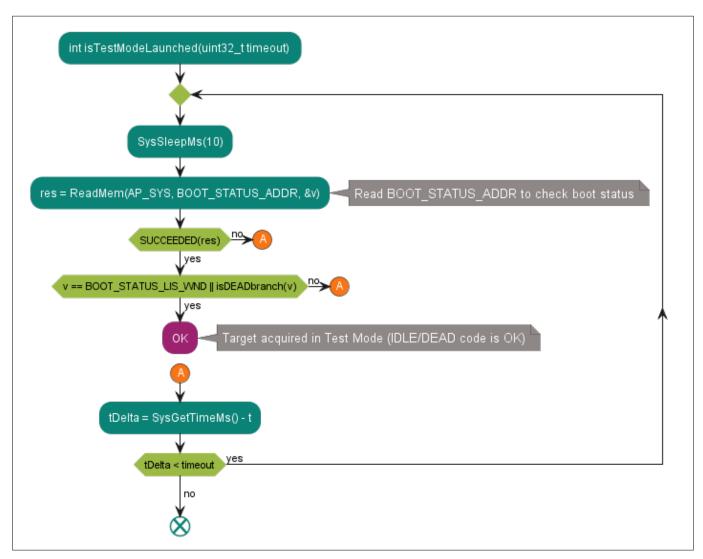

Figure 17 Test mode acquisition flowchart

002-38998 Rev. \*C

#### 5 Acquisition algorithm

Figure 18 Flowchart for step 2 - acquire in test mode

See the code example in AcquireTestMode

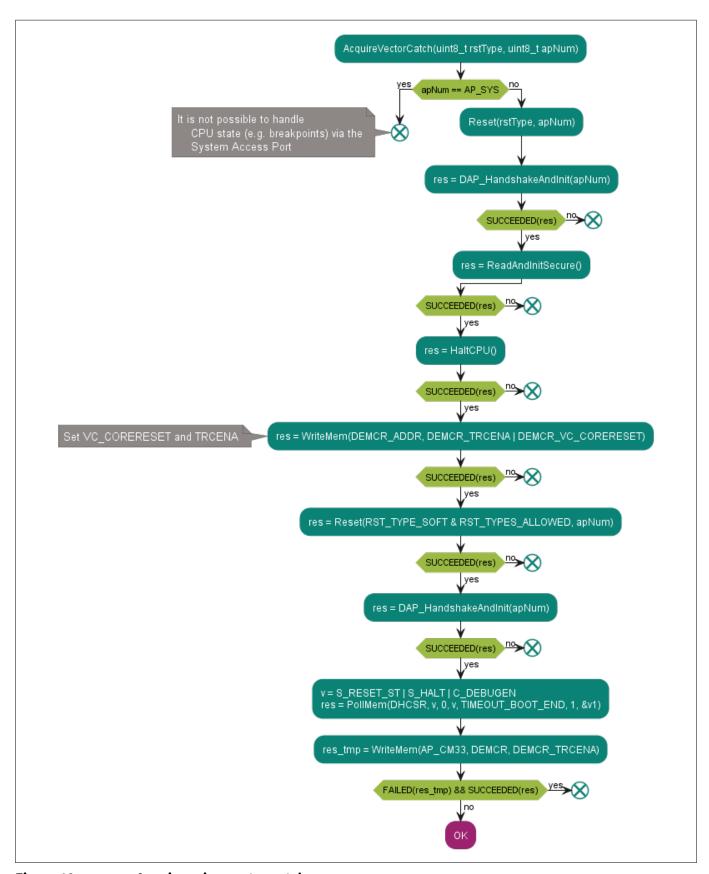

## 5.3.3 Step 3 – acquire PSOC™ Control C3 MCU using vector catch

The "acquire chip" sequence in the previous section is based on entering the PSOC™ Control C3 MCU test mode by triggering a hard-reset condition, and then sending the acquire sequence within the specified time window. The hard-reset condition is generated by toggling either the XRES pin or the power supply to the device. Programming by entering test mode using XRES or power cycling is the recommended method for third-party production programmers or any other general-purpose programmer.

There might be cases where the host programmer hardware or software constraints might prevent programming of the device in test mode. These constraints can include:

- The host programmer hardware might be I/O-pin-constrained and cannot spare an extra I/O for toggling the XRES pin or the power supply to the MCU. Only the SWJ protocol pins are available for programming

- The host programmer software application is unable to meet the timing requirements to enter test Mode after triggering a hard-reset condition. In such a scenario, the MCU enters the user code execution mode after the test mode timing window elapses

For a host programmer with any of these constraints, the modified acquire-chip sequence provided in this section does not require XRES/power supply toggling, and it does not have the test-mode timing requirements.

#### **Programming specification**

#### 5 Acquisition algorithm

Only the SWJ protocol pins are used for programming. This modified sequence works only under the following conditions:

- The SWJ pins on the MCU have not been repurposed for any other application-firmware-specific use. If the SWJ pins are repurposed as part of the existing firmware image in the flash, the SWJ pins are not available for communication with the host SWJ interface to update the existing firmware image

- The access restriction properties allow the SWJ access to the access debug ports (normal access restriction properties are applicable if the device is in the normal protection state, secure, and dead access restriction properties are applicable if the device is in the secure and dead protection states respectively)

Developers wanting to program devices using the modified sequence should be aware of these limitations. Devices coming from the factory satisfy both these conditions, and therefore, can be programmed using the modified acquire sequence. However, if firmware that does not meet any of these conditions, then the devices are programmed to the MCU, subsequent re-programming of the device is not possible using the modified acquire sequence. Due to this limitation, this method is not recommended for third-party programmers or general-purpose programmers because they would generally be required to support programming under all possible operating conditions.

#### 5 Acquisition algorithm

Figure 19 Acquire using vector catch

#### **Programming specification**

5 Acquisition algorithm

#### 5.4 Unlock the access to the CPU (helper functions)

The Cortex<sup>®</sup>-M33 access port can be disabled by the access restrictions policy. The access port can be either temporarily or permanently disabled. If temporarily disabled, it can be re-enabled using the debug certificate.

Certificate cannot override the access port that is permanently disabled by access restrictions. Note:

The Boot ROM verifies the certificate; if the verification is successful, it enables CM33-AP as specified in the certificate.

Procedure of opening CM33-AP using debug certificate:

- RAM: Sys-AP must be enabled to load the debug certificate directly into the RAM which is reserved by Boot ROM at the end of RAM. This flow can be used to debug CM33 core. Flow details:

- a. The debugger sets the appropriate BOOT\_DLM\_CTL.REQUEST and issues a software reset by setting RES\_SOFT\_CTL.TRIG\_SOFT = 1

- The Boot ROM resets, detects BOOT\_DLM\_CTL.REQUEST, and sets BOOT\_DLM\_CTL.WFA, thus, b. indicating that it waits for a certificate loaded

- The debugger loads the debug certificate into the RAM using Sys-AP. The address of the certificate c. loaded must be placed at BOOT DLM CTL 2. After all, the debugger sets BOOT\_DLM\_CTL.REQUEST again to trigger the verifying certificate

- Boot ROM can now verify the debug certificate d.

- If verification is successful, the appropriate APs are enabled e.

#### 5 Acquisition algorithm

#### 5.4.1 WaitForWFAMode

Figure 20 Wait for the device to enter WFA mode

This is a helper function used in the AcquireInWFAMode subroutine. It polls the BOOT\_DLM\_CTL register waiting for the Boot ROM to enter WFA mode. In WFA mode, the Boot ROM is spinning in the IDLE loop waiting for the debug certificate to be loaded by the debugger.

See the code example in WaitForWFAMode.

5 Acquisition algorithm

## 5.4.2 AcquireInWFAMode

Figure 21 Acquire the device and wait for WFA mode

This function acquires the device in WFA mode and waits for the Boot ROM to be ready to accept the debug certificate. The debugger sets the appropriate BOOT\_DLM\_CTL.REQUEST and issues a software reset by setting RES\_SOFT\_CTL.TRIG\_SOFT = 1.

See the code example in AcquireInWFAMode.

5 Acquisition algorithm

## 5.4.3 LoadDebugCert

Figure 22 Loads the debug certificate to the RAM

Reads the debug certificate and loads its contents to the RAM. See the code example in LoadDebugCert.

5 Acquisition algorithm

#### 5.4.4 StartWFARequest

Figure 23 Executes the WFA request

StartWFA request is executed after debug certificate is loaded at DEBUG\_CERT\_ADDR (and that address is also written to BOOT\_DLM\_CTL\_2). In fact, WFA bit is now cleared to let ROM APP start reading certificate. As an indication of successful result – CM33 access point must appear in a scanning list.

See the code example in StartWFARequest.

# infineon

#### 5 Acquisition algorithm

# 5.5 Unlock the access to the CPU using the debug certificate

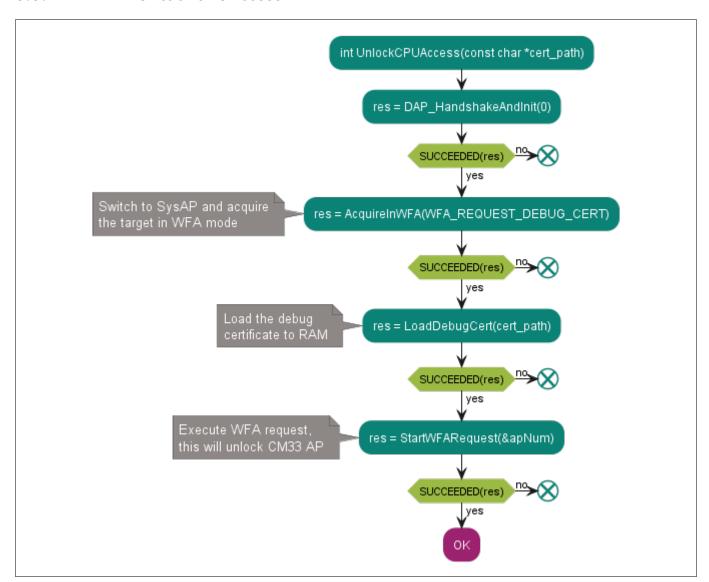

## 5.5.1 UnlockCPUAccess

Figure 24 Unlocks the access to the CM33 access port

This function performs the whole unlock sequence described in Unlock the access to the CPU (helper functions). After running this function, the device is reset and CM33 access port is opened by the Boot ROM. The CPU is not halted after the reset, so it starts to execute the application code. This is sufficient for the debugger to attach to the running target and observe its state.

See the code example in UnlockCPUAccess.

## **Programming specification**

#### 6 Using SROM APIs to program/erase flash

# 6 Using SROM APIs to program/erase flash

As described in Acquisition algorithm, SROM API must be called after successful acquisition. SROM APIs function calling is performed by means of setting the appropriate registers of the CM33 processor as follows:

- pc program counter

- sp stack pointer

- lr linked register

- r0, r1, r2 general registers

The program counter value is filled with a pointer (see Table 2), depending on a desired operation. General registers hold the parameters of a SROM API. A linked register stores an address in RAM where breakpoint assembler operation code is stored. A stack pointer should contain an address of RAM, so that the function can have adequate size of memory for its operation.

Note that the data is flashed in chunks of 512 bytes. Smaller data cannot be flashed or erased. Also, functions work in blocking mode; therefore, the CPU cannot be utilized while flash operations are fulfilled.

# 6.1 SROM erases API usage

The pseudocode for SROM erase API utilization is shown in Erase API usage pseudocode. Erase SROM API erases one row of flash at a given address. The code snippet provides a method where Ir holds an address of RAM when breakpoint is stored; therefore, the processor halts itself from letting know that the function is done. If the full size of flash is inserted, as shown in the code snippet Erase API usage pseudocode, the example application erases the entire flash.

# 6.2 SROM program API usage

The pseudocode for SROM program API utilization is shown in Program API usage pseudocode. It shows how to set core registers, where data to be written, flash context, and break pointer operation to RAM to achieve image flashing are included. Dividing the hexadecimal file into parts of 512 bytes and incrementing the start of flash bank, the entire image is programmed into flash.

## **Programming specification**

7 Appendix A: Intel hex file format

# 7 Appendix A: Intel hex file format

Intel hex file records are a text representation of hexadecimal-coded binary data. Only ASCII characters are used, so the format is portable across most computer platforms. Each line (record) of Intel hex file consists of six parts, as shown in Figure 25.

| Start Code (Colon Byte Count | Address (2 bytes) | Record Type | Data      | Checksum |

|------------------------------|-------------------|-------------|-----------|----------|

| Character) (1 byte)          |                   | (1 byte)    | (N bytes) | (1 byte) |

#### Figure 25 Hex file record structure

**Start code**, one character - an ASCII colon (:)

- Byte count, two hex digits (1 byte) specifies the number of bytes in the data field

- Address, four hex digits (2 bytes) a 16-bit address of the beginning of the memory position for the data

- **Record type**, two hex digits (00 to 05) defines the type of the data field. The record types used in the hex file generated by Infineon are as follows:

- 00 Data record, which contains the data and 16-bit address

- 01 End of file record, which is a file termination record and has no data. This must be the last line of the file; only one is allowed for every file

- 04 Extended linear address record, which allows full 32-bit addressing. The address field is 0000, the byte count is 02. The two data bytes represent the upper 16 bits of the 32-bit address, when combined with the lower 16-bit address of the 00-type record

- **Data**, a sequence of 'n' bytes of the data, represented by 2n hex digits

- **Checksum**, two hex digits (1 byte), which is the least significant byte of the two's complement of the sum of the values of all fields except fields 1 and 6 (start code ':' byte and two hex digits of the checksum)

Examples for the different record types used in the hex file generated for the PSOC™ Control C3 MCU are as follows:

Consider that these three records are placed in consecutive lines of the hex file (chip-level protection and end of hex file).

:0200000490600A

:0100000002FD

:0000001ff

For the sake of readability, "record type" is highlighted in red and the 32-bit address of the chip-level protection is in blue.

The first record (:0200000490600A) is an extended linear address record as indicated by the value in the record type field (04). The address field is 0000, the byte count is 02. This means that there are two data bytes in this record. These data bytes (0x9060) specify the upper 16 bits of the 32-bit address of data bytes. In this case, all the data records that follow this record are assumed to have their upper 16-bit address as 0x9060 (in other words, the base address is 0x90600000). OA is the checksum byte for this record:

0x0A = 0x100 - (0x02+0x00+0x00+0x04+0x90+0x60).

The next record (:0100000002FD) is a data record, as indicated by the value in the record type field (00). The byte count is 01, meaning there is only one data byte in this record (02). The 32-bit starting address for these

## **Programming specification**

## 7 Appendix A: Intel hex file format

data bytes is at address 0x90600000. The upper 16-bit address (0x9060) is derived from the extended linear address record in the first line; the lower 16-bit address is specified in the address field of this record as 0000. FD is the checksum byte for this record.

The last record (:00000001FF) is the end-of-file record, as indicated by the value in the record type field (01). This is the last record of the hex file.

## **Programming specification**

#### 8 Appendix B: Serial wire debug (SWD) protocol

# 8 Appendix B: Serial wire debug (SWD) protocol

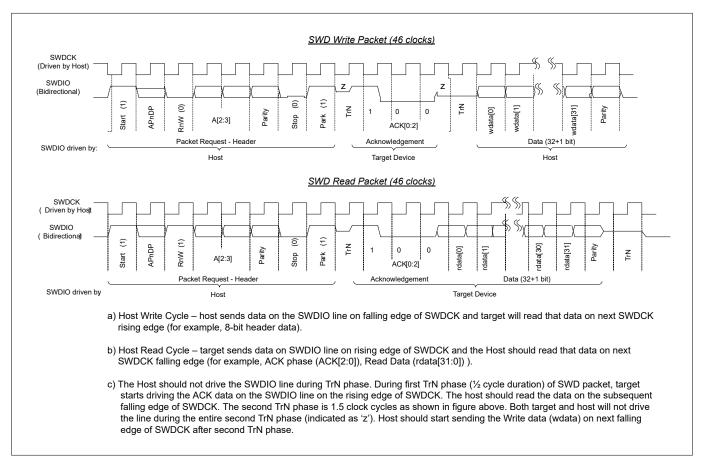

The SWD protocol is a packet-based serial transaction protocol. At the pin level, it uses a single bidirectional data connection (SWDIO) and a clock connection (SWDCK). The host programmer always drives the clock line, while either the programmer or the PSOC™ Control C3 MCU drives the data line. A complete data transfer (one SWD packet) requires 46 clocks and consists of three phases:

- Packet Request The host programmer issues a request to the PSOC™ Control C3 MCU (silicon)

- Acknowledge Response The PSOC™ Control C3 MCU (silicon) sends an acknowledgement to the host

- **Data Transfer Phase** The data transfer is either from the PSOC™ Control C3 MCU to the host, following a read request (RDATA), or from the host to the PSOC™ Control C3 MCU, following a write request (WDATA). This phase is present only when a packet request phase is followed by a valid (OK) acknowledge response

Figure 26 shows the timing diagrams of the read and write SWD packets.

## Figure 26 Write and read SWD packet timing diagrams

The SWD packet is transmitted in the following sequence:

- The start bit initiates a transfer; it is always logical '1'

- The APnDP bit determines whether the transfer is an AP access (indicated by '1') or a DP access (indicated by '0')

- The next bit is RnW, which is '1' for read from the MCU or '0' for a write to the MCU

The ADDR bits (A[3:2]) are register select bits for the access port or debug port. See Table 3 for register definition.

• The parity bit contains the parity of APnDP, RnW, and ADDR bits. This is an even parity bit. If the number of logical 1s in these bits is odd, then the parity must be '1', otherwise it is '0'

## **Programming specification**

#### 8 Appendix B: Serial wire debug (SWD) protocol

- If the parity bit is not correct, the PSOC™ Control C3 MCU ignores the header and there is no ACK response. From the host standpoint, the programming operation should be aborted and retried by doing a device reset

- The stop bit is always logic '0'

- The park bit is always logic '1' and should be driven high by the host

The ACK bits are device-to-host response. Possible values are shown in Table 6. Note that ACK in the current SWD transfer reflects the status of the previous transfer. 'OK ACK' means that the previous packet was successful. WAIT response requires a data phase, as explained in the following list. For a FAULT status, the programming operation should be aborted immediately.

- For a WAIT response, if the transaction is a read, the host should ignore the data read in the data phase. The PSOC™ Control C3 MCU does not drive the line and the host must not check the parity bit as well

- For a WAIT response, if the transaction is a write, the data phase is ignored by the PSOC™ Control C3 MCU. However, the host must still send the data to be written from the standpoint of implementation. The data parity bit corresponding to the data should also be sent by the host

- For a WAIT response, it means that the PSOC™ Control C3 MCU is processing the previous transaction. The host can try for a maximum four continuous WAIT responses to see if an OK response is received. If it fails, then the programming operation should be aborted and retried

- For a FAULT response, the programming operation should be aborted and retried by doing a device reset

# Table 6 ACK response for SWD transfers

| ACK[2:0] | SWD |

|----------|-----|

| ОК       | 001 |

| WAIT     | 010 |

| FAULT    | 100 |

| NACK     | 111 |

- The data phase includes a parity bit (even parity)

- For a read packet, if the host detects a parity error, then it must abort the programming operation and try again

- For a write packet, if the PSOC™ Control C3 MCU detects a parity error in the data sent by the host, it generates a FAULT ACK response in the next packet

Turnaround (TrN) phase: There is a single-cycle turnaround phase between the packet request and the ACK phases, as well as between the ACK and data phases for write transfers as shown in Figure 26. According to the SWD protocol, both the host and the PSOC™ Control C3 MCU use the TrN phase to change the drive modes on their respective SWDIO lines. During the first TrN phase after packet request, the PSOC™ Control C3 MCU starts driving the ACK data on the SWDIO line on the rising edge of SWDCK in the TrN phase. This ensures that the host can read the ACK data on the next falling edge. Thus, the first TrN cycle lasts for only a half-cycle duration. The second TrN cycle of the SWD packet is one and one-half cycle long. Neither the host nor the PSOC™ Control C3 MCU should drive the SWDIO line during the TrN phase, as indicated by 'z' in Figure 26.

- The address, ACK, and read and write data are always transmitted LSB first

- According to the SWD protocol, the host can generate any number of SWD clock cycles between two

packets with the SWDIO LOW. You should generate several dummy clock cycles (three) between two

packets or make the clock free running in IDLE mode

**Note**: The SWD interface can be reset by clocking 50 or more cycles with the SWDIO kept HIGH. To return to the idle state, SWDIO must be clocked LOW once.

# infineon

9 Appendix C: Joint Test Action Group (JTAG) protocol

# 9 Appendix C: Joint Test Action Group (JTAG) protocol

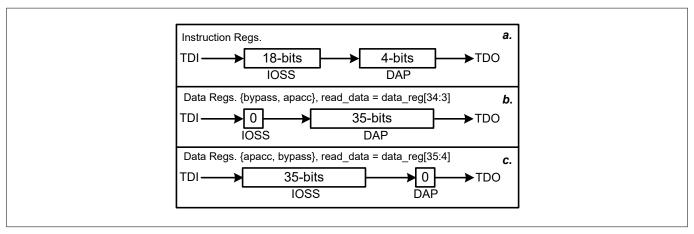

The PSOC™ Control C3 MCU JTAG interface complies with the IEEE 1149.1 specification and provides additional instructions. There are two TAPs in the silicon:

- In IOSS for boundary scan

- In CPUSS DAP (IDCODE 0x4BA06477) for device debugging and programming

The two TAPs are connected in series, where TDO of the IOSS TAP is connected to TDI of the DAP TAP. See Figure 27.

Figure 27 IOSS/DAP TAP connection

Each TAP consists of a 35-bit data register (called DP/AP access register). The size of the instruction register is 4 bits for the DAP TAP and 18 bits for the IOSS TAP. The important instructions to program the device through JTAG are listed in Table 7.

Table 7 PSOC™ Control C3 MCU JTAG instructions

| Bit Code [3:0] | Instruction | PSOC™ Control C3 MCU function                                                                      |  |  |

|----------------|-------------|----------------------------------------------------------------------------------------------------|--|--|

| 1110           | IDCODE      | Connects TDI and TDO to the device 32-bit JTAG ID code                                             |  |  |

| 1010           | DPACC       | Connects TDI and TDO to the DP/AP access register (35-bit) for access to the debug port registers  |  |  |

| 1011           | APACC       | Connects TDI and TDO to the DP/AP access register (35-bit) for access to the access port registers |  |  |

| 1111           | BYPASS      | Bypasses the device by providing a 1-bit latch (bypass register) connected between TDI and TDO     |  |  |

If an instruction that is not applicable is shifted into a TAP, the TAP goes into bypass mode. In bypass mode, the data register is only 1-bit long with the contents of 0. The bypass mode is used to isolate the PSOC™ Control C3 MCU TAP. For example, if targeting the IOSS TAP, the DAP TAP is put in bypass mode by shifting in the BYPASS instruction into its instruction register and if targeting the DAP TAP, the IOSS TAP will be placed in bypass mode. See the examples of TAP configuration in Figure 28.

## **Programming specification**

## 9 Appendix C: Joint Test Action Group (JTAG) protocol

Figure 28 IOSS/DAP TAP configuration examples

- Combines instruction registers; 22 bits total

- Enables access to the APACC registers of the DAP for device debugging and programming and configures the IOSS TAP in bypass mode; 36 bits total

- Enables access to the IOSS APACC registers for enabling test modes and configures the DAP TAP in bypass mode; 36 bits total

# 10 Appendix D: Code example

# 10.1 Hardware-specific backend functions

The following code example is written in hardware-independent way so that it relies on a few backend functions which must be implemented by the user. Implementation of these functions will be different across different debug adapters and different operating systems.

This code expects that the following functions are available during linking:

# 10.1.1 extern int IsJTAG(void);

```

/*********

* Returns any non-zero value if underlying transport is JTAG (zero for SWD).

*/

extern int IsJTAG(void);

```

# 10.1.2 extern int SetXRES(state);

# 10.1.3 extern int SetVoltage(voltage);

```

/***********

* Controls the voltage supplied by the debug adapter to power the target MCU.

* This function is optional and should return Error if not implemented.

* Parameters:

* voltage - output voltage, in millivolts

* Return value:

* zero - 0.K.

* non-zero - Error

*/

extern int SetVoltage(uint32_t voltage);

```

# 10.1.4 extern int SWJSequence(out\_bits, num\_bits);

# 10.1.5 extern int Read/WriteDAP(reg, ap\_n\_dp, value);

```

* Reads (or Writes) data to CoreSight registers.Pay attention, PSoC Control C3 is based on

ADIv6 debug interface.

* Parameters:

reg - register address

For Read operation this parameter should take one of the following values:

- DP REG DPIDR

- DP_REG_CTRL_STAT 0x04

- DP_REG_SELECT 0x08

0xD00

- AP_REG_CSW

- AP_REG_TAR

0xD04

AP_REG_DRW

0xD0C

For Write operation this parameter should take one of the following values:

- DP_REG_ABORT

- DP_REG_CTRL_STAT 0x04

- DP_REG_SELECT 0x08

- DP_REG_RDBUFF

0x0C

0xD00

AP_REG_CSW

- AP_REG_TAR

0xD04

- AP_REG_DRW

0xD0C

ap_n_dp - '1' for AP registers, '0' for DP registers

value - value to write (or pointer to the variable where read result will be stored)

* Return value:

zero - O.K.

non-zero - Error

extern int ReadDAP(uint8_t reg, uint8_t ap_n_dp, uint32_t* value);

extern int WriteDAP(uint8_t reg, uint8_t ap_n_dp, uint32_t value);

```

# 10.1.6 extern void SysSleepMs(uint32\_t msec);

# 10.1.7 extern int SysGetTimeMs(void);

```

/*********

* Returns the number of milliseconds that have elapsed since some fixed time point in the past.

*

* Parameters:

* none

*

* Return value:

* number of milliseconds

*/

extern int SysGetTimeMs(void);

```

## 10.2 Constants and static data used in code

#### 10.2.1 Constants

```

/* --- Target acquisition methods --- */

/* Initial check whether boot code is already in IDLE or DEAD branch */

#define ACQUIRE_CHECK_IDLE (1 << 0)</pre>

/* Test mode (TM) acquisition (recommended) */

#define ACQUIRE_TEST_MODE

(1 << 1)

/* Vector Catch */

#define ACQUIRE VECTOR CATCH (1 << 2)</pre>

#define ACQUIRE_METHOD_ALLOWED (ACQUIRE_TEST_MODE | ACQUIRE_VECTOR_CATCH )

/* --- MCU reset types --- */

/* Hardware reset (XRES)*/

#define RST TYPE XRES

(1 << 0)

/* Hardware reset (Power Cycle) */

#define RST TYPE POWER

(1 << 1)

/* Software reset (RES_SOFT_CTL.TRIGGER_SOFT) */

#define RST_TYPE_RES_SOFT_CTL (1 << 2)</pre>

/* Software reset (AIRCR.SYSRESETREQ) */

#define RST_TYPE_SYSRESETREQ (1 << 3)</pre>

/* Software reset (DP->CTRL/STAT.CDBGRSTREQ) */

#define RST_TYPE_CDBGRSTREQ (1 << 4)</pre>

(RST_TYPE_RES_SOFT_CTL | RST_TYPE_SYSRESETREQ |

#define RST_TYPE_SOFT

RST TYPE CDBGRSTREQ)

#define RST TYPE HARD

(RST TYPE XRES | RST TYPE POWER)

#define RST_TYPE_ANY

(RST_TYPE_HARD | RST_TYPE_SOFT)

#define RST_TYPE_ALLOWED \

(RST_TYPE_XRES | RST_TYPE_RES_SOFT_CTL | RST_TYPE_SYSRESETREQ | RST_TYPE_CDBGRSTREQ)

/* --- Access Ports --- */

/* AP[0] System Access Port*/

#define AP_SYS

/* AP[1] Cortex-M33 Access Port */

#define AP CM33

/* Maximum number of Access Ports */

#define AP_MAX

/* Prefered Access Port (AP[1] - CM33 Core is used by default in this script) */

#define AP_TO_USE

/* "0" - Can use any available AP if needed; "1" - Strict AP usage to preferred only*/

#define AP_TO_USE_STRICT

/* AP cpu num for psoc c3 in ADIv6*/

/* AP Sys num for psoc c3 in ADIv6*/

static const uint32 t AP ADDR[] = { /* Array of AP adresses: */

AP_SYS_ADIV6, /* Address of System Access Port - AP[0] */

AP CM33 ADIV6 /* Address of Cortex-M33 Access Port - AP[1] */

```

## **Programming specification**

```

};

/* --- AP/DP registers --- */

/* DP IDCODE 0x4C013477 for SWD or 0x4BA06477 for JTAG */

#define DP IDCODE MSK

0xF0000FFF

#define DP_IDCODE_VAL

0x40000477

(3u << 2u) /* Mask for Bits[3:2] of the AP register address */

#define AP REG A3A2 MSK

0xFFFFFF0 /* Mask for bits[31:4] of DP->SELECT register */

#define DP_SELECT_MSK

#define APV2 REG CSW

/* Offset of AP->CSW register (Adiv6)*/

0xD00

#define APV2 REG TAR

0xD04

/* Offset of AP->TAR register (Adiv6)*/

0xD0C

#define APV2 REG DRW

/* Offset of AP->DRW register (Adiv6)*/

#define AP CSW PROT MSK

(0x4F<<24) /* 0x4F000000:Bus access protection control mask. */

#define AP_CSW_SIZE_WORD

(2 << 0)

/* Bus access protection control for Secure access */

#define AP CSW PROT VAL

(0x0B<<24)

/* Bus access protection control for Non Secure access. */

#define AP_CSW_PROT_NS_VAL

(0x4B<<24)

/* --- Target-specific registers and definitions --- */

/* Boot status result address */

#define BOOT STATUS ADDR

0x52200418

/* SRSS->TST_MODE: Test Mode Control Register */

#define TST MODE

0x52200400

/* SRSS->TST_MODE.TEST_MODE (bit[31], 0x80000000):

* 1 - Indicates the chip is in test mode. 0 - Normal operation mode */

#define TST_MODE_TEST_MODE

(1 << 31)

/* RES_SOFT_CTL: Soft Reset Trigger Register */

#define RES SOFT CTL

0x52200410

/* RES_SOFT_CTL.TRIG_SOFT (bit[0]): Triggers a soft reset. The reset clears this bit.*/

#define RES SOFT CTL TRIG SOFT (1 << 0)

/* -- WFA acquiring, sending debug token -- */

/* Register to ser type of request to bootROM */

/* set WFA_REQUEST_DEBUG_CERT here for WFA acquiring with debug certificate */

#define BOOT DLM CTL

0x52200404

#define BOOT_DLM_CTL_WFA_MASK

0x80000000

/* Holds address of debug certificate, set DEBUG_CERT_ADDR during WFA acquiring here*/

#define BOOT DLM CTL 2

0x52200408

/* BootROM sets status after WFA request*/

#define BOOT_DLM_STATUS

0x5220040C

/* Possible values for BOOT DLM STATUS: */

#define DEBUG CER VERIFICATION SUCCESS 0x0D500084

#define CYBOOT WFA POLLING

0x0D500080

/* Long-style namings*/

#define SRSS_RES_SOFT_CTL

RES_SOFT_CTL

```

## **Programming specification**

```

#define SRSS_RES_SOFT_CTL_TRIG_SOFT RES_SOFT_CTL_TRIG_SOFT

#define SRSS_TST_MODE

TST MODE

#define SRSS_TST_MODE_TEST_MODE

TST MODE TEST MODE

/* Mask for MODULE_ID in status word */

#define CYBOOT ID MSK

0xFFF00000

/* The module IDs for BootROM in case of success */

#define CYBOOT ID SUCCESS

0x0D500000

/* The module IDs for BootROM in case of fail */

#define CYBOOT ID FAIL

0xBAF00000

/* Mask for RESULT_CODE (status) in status word */

#define CYBOOT STATUS MSK

/* Result code indicating BootROM launched the application */

#define CYBOOT_NEXT_APP_LAUNCHED

0x0D500067

/* Result code indicating BootROM reached IDLE branch */

#define CYBOOT IDLE BRANCH REACHED

0x0D500068

#define BOOT STATUS LIS WND

CYBOOT IDLE BRANCH REACHED

#define CYBOOT_DEBUG_TOKEN_PASSED

0x0D500084 /* Debug token verified */*/

#define CYBOOT_DEBUG_TOKEN_FAILED

0x0D500085 /* Debug token verification failed */

#define CYBOOT_IMG_INVALID

0xBAF000A0 /* Image invalid/erased flash*/

#define CYBOOT_SUCCESS

0x0D50B002

#define CYBOOT SUCCESS 1

0x05501000

#define CYBOOT SUCCESS 2

0x0800A002

#define CYBOOT_BAD_PARAM

0xBAF00001

#define CYBOOT LOCKED

0xBAF00002

#define CYBOOT_STARTED

0xBAF00003

#define CYBOOT_FINISHED

0xBAF00004

#define CYBOOT CANCELED

0xBAF00005

#define CYBOOT TIMEOUT

0xBAF00006

#define CYBOOT_NOT_IMPLEMENTED

0xBAF00007

#define CYBOOT FAILED

0xBAF00008

#define CYBOOT L1 APP DESCR INVALID

0xBAF00011

#define CYBOOT_SERV_APP_DESCR_INVALID